仇天元

The pronunciation of my Chinese name is “Chyoh Tyen Ywen” (Mandarin Pinyin: Qíu Tiān Yuán).

About Me

I am currently a Ph.D. student in ECE (PurNET Lab) at Purdue University, advised by Prof. Xiaoqi Chen, with a focus on research in computer networking systems.

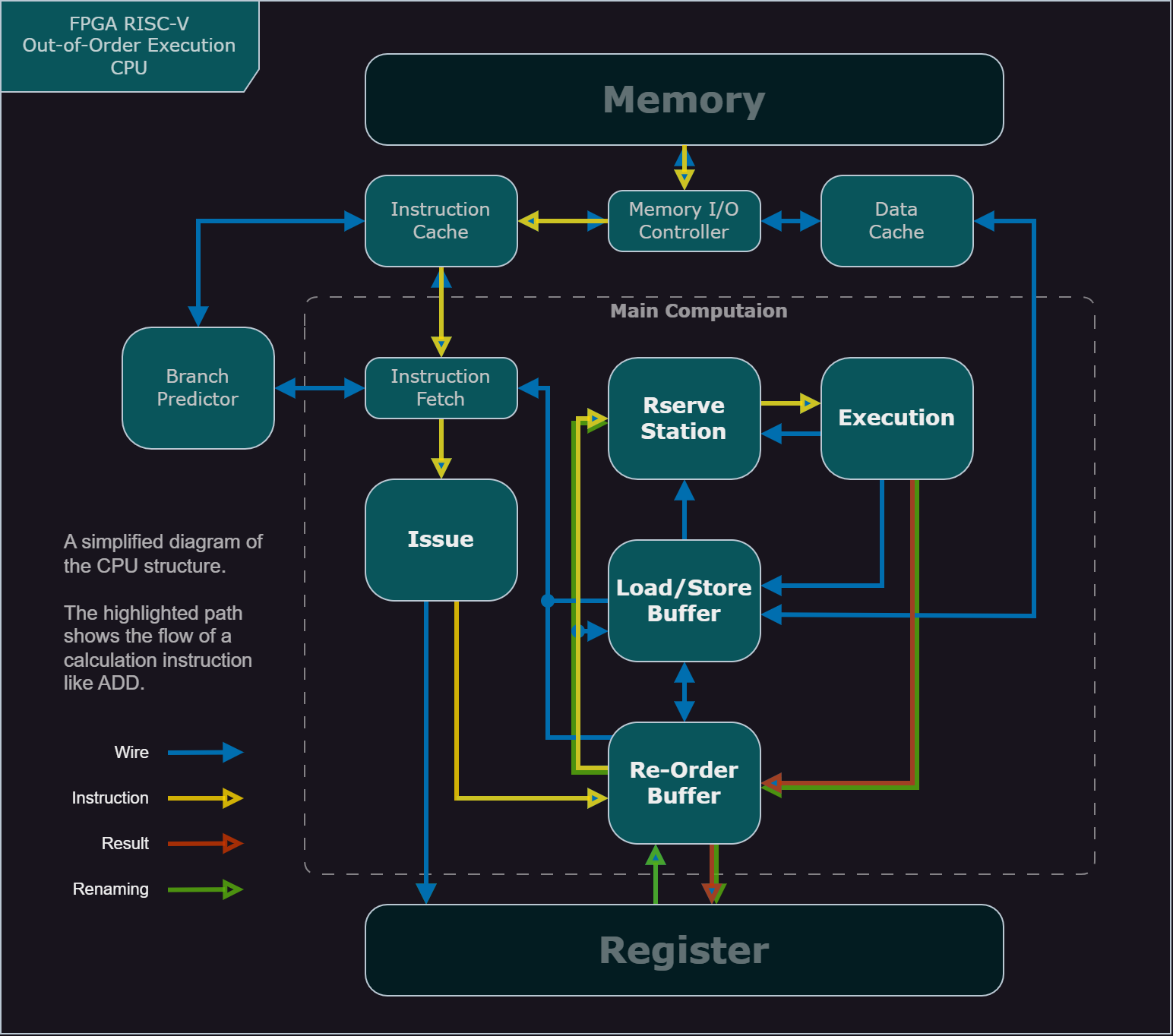

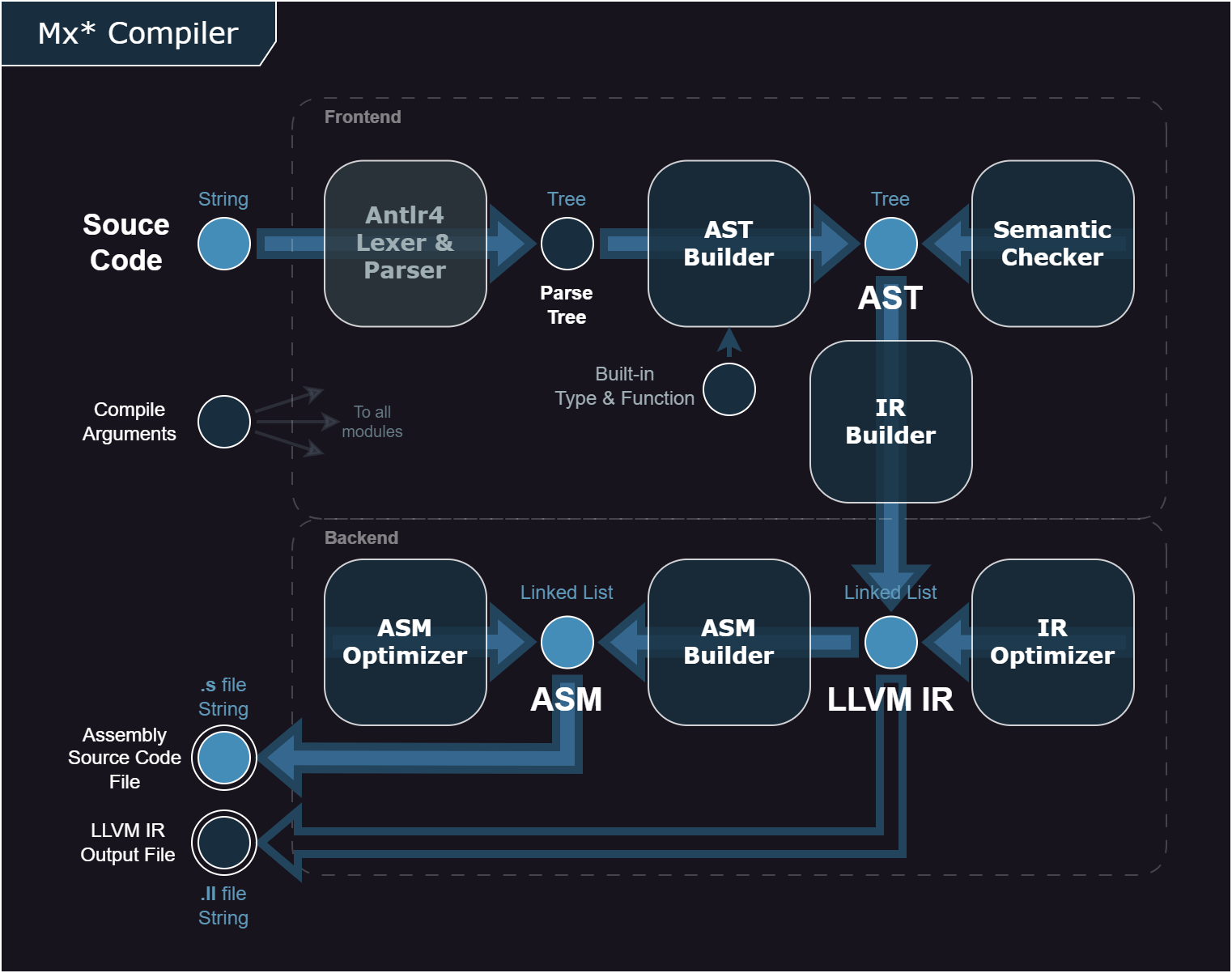

My research interests span systems, networking, and machine learning. I am particularly drawn to a bottom-up research approach that starts from the behavior of hardware components such as FPGAs and PCIe, extends through intermediate layers like operating systems and compilers, and reaches applications like machine learning. This holistic perspective enables me to identify performance gaps between layers and explore optimizations through innovative system design. My work broadly covers emerging challenges in networking and machine learning system, including FPGA-based SmartNIC, GPU, and distributed training of LLM. I am also open to exploring a range of topics in the broader systems field, from serverless to database.

I earned my Bachelor’s degree in CS (Zhiyuan Honors Program) from the ACM Class, Zhiyuan College, at Shanghai Jiao Tong University. During my undergraduate, I interned as a research assistant of DSL at the University of Pennsylvania, where I was mentored by Prof. Vincent Liu and Ph.D. Liangcheng Yu. Our research focused on FPGA-based SmartNICs and PCIe systems. Prior to that, I completed an internship as a research assistant in the field of computer vision under Prof. Li Niu, working on diverse image harmonization.

This page was updated in January 2025.

Selected Projects

Some bachelor period course projects. Each project listed was crafted solely by myself and from scratch. Several projects include third-party libraries.

- Developed a reimplementation of basic part of C++ Standard Library with additional functions, written in C++.

- Implemented A program for reading, parsing, converting, and performing model checking of linear temporal logic formulas, written in Java.

Experience

DSL, University of Pennsylvania

August 2023 - December 2023

Research Assistant, advised by Prof. Vincent Liu

Philadelphia, Pennsylvania, US

- Investigated co-design of the FPGA-based SmartNIC and the host networking stack.

- Leverage idle PCIe transactional bandwidth to mitigate host congestion.

- Optimize tail latencies for high-level applications.

BCMI, Shanghai Jiao Tong University

July 2022 - July 2023

Research Assistant, advised by Prof. Li Niu

Shanghai, China

- Proposed a deep learning network of image harmonization guided by reflectance.

- Designed a diverse reflectance generation network to predict a variety of plausible foreground reflectances.

- Enabled multiple plausible image harmonization results using the outputs from the generation network.

Zhiyuan College, Shanghai Jiao Tong University

September 2021 - June 2023

Teaching Assistant

Shanghai, China

- CS1953 Programming, Fall 2021

- CS1952 Programming Practice, Summer 2022

- CS2951 Computer Architecture, Fall 2022

- CS2952 Operating System, Spring 2023

Skills

-

Engineering: Exceptional code style, document writing, and version control. Proficient in both Windows and Linux environments. Experienced with industry toolchains and documentation (Vivado).

-

Programming: Proficient in algorithm, data structure, modern programming language features (e.g. C/C++, Rust, Python, Java), HDL (Verilog), database (MongoDB), utility programs (e.g. MATLAB, Visual Basic, Unity, Processing).

-

Administration: Served as the class representative and public relation officer of Zhiyuan honors college student union.

More than coding

My life’s ambition is to make the world a better place with more humanistic care.

For my hobbies, I’ve always been passionate about learning new knowledge from science and engineering to humanities and arts, and different cultures all around the world. I especially like music (e.g. J-pop, J-rock), graphic design (e.g. poster, font), animation, game as art, and different beverages (e.g. soda, whiskey, cocktail, coffee).

Since arriving in Indiana, I have chances to engage more in some localized hobbies, like karting, snowboarding, and figure skating! And I’m quite looking forward to a road trip around the entire country!

Here is a simple work written in Processing many years ago.